# Ultra-Low Latency FPGA Solution for Electronic Trading and Networking Applications

White Paper – Intel PSG Arria-10 FPGA

# Introduction

**REFLEX CES** and **Orthogone Technologies** collaborated to offer an ultra-low latency networking solution for electronic trading. The solution is a low-profile PCIe Network Processing FPGA board based on Intel Arria-10 FPGA. The board has many salient features, including two QSFP+ ports with integrated ultra-low latency 10G MAC/PCS IP cores, 4GB of DDR4 memory, up to 144Mb of QDR2+ and a PCIe Gen. 3 x 8 interface. This makes it an ideal solution for FPGA accelerated Tick-to-Trade systems or market data feed handlers. Other applications such as High Performance Computing (HPC), networking functions and HW acceleration can also be implemented with this solution.

This white paper will present an overview of the solution developed and the comprehensive reference design that is offered to rapidly enable customers to build their trading infrastructure and networking components. Latency and network throughput performances are presented in detail and backed with lab measurements confirming the performances.

## **Solution Overview**

The XpressGXA10-LP1150 low-profile PCIe Network Processing FPGA card includes an Intel (Altera) 10AX115 Arria-10 FPGA. The board is available in three options (Basic, Ultra, and Turbo), allowing the customers to select amongst various memory configurations and FPGA speed grades. A one PPS (Pulse-per-second) input is available for an application requiring inter-board time synchronization. The Turbo version features an FPGA with -1 core speed grade enabling the customers to take advantage of the fastest FPGA fabric and optimize latency, as well as throughput performances.

A photograph of the XpressGXA10-LP1150 low-profile PCIe board is illustrated below.

Figure 1: REFLEX CES XpressGXA10-LP1150 Low-Profile PCIe Board

A comprehensive documentation package and a Board Support Package (BSP) are provided to enable rapid deployment of the solution. Additional information is available on REFLEX CES website: <u>https://www.reflexces.com/products/boards/pcie/xpressgxa10-lp1150</u>

# **10G MAC/PCS/PMA Reference Design Overview**

Orthogone has developed an ultra-low latency 10G Ethernet MAC/PCS/PMA solution specifically designed for applications such as Electronic/High Frequency Trading. The core is designed to take advantage of the GX transceiver low latency and the fast core fabric offered by the -1 speed grade of the Intel Arria-10 FPGA.

A multi-port 10G MAC reference design tailored to the XpressGXA10-LP1150 board has been fully validated and characterized. A simple Verilog parameter allows the customers to select the number of 10G ports (1 - 4) to be instantiated per QSFP+. The reference design includes all the key components required to rapidly build low-latency Ethernet interfaces. The Arria-10 transceivers, the calibration modules, the clocks and PLL, the reset sequence, and the IP cores are automatically generated to rapidly enable a very flexible and reliable solution.

The reference design also includes test modules such as packet generator and analyzer, and CPU interface that are provided as clear Verilog code. All the necessary timing constraints and make files are provided to re-compile the reference design and ensure repeatable functionalities and performances.

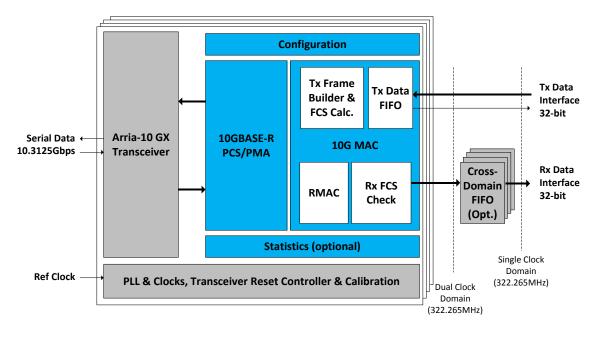

A block diagram of the MAC/PCS/PMA solution is presented in the next figure (a 4-port configuration is illustrated). The modules highlighted in blue are generally provided as encrypted source code while the others are provided as clear Verilog.

Figure 2: Orthogone Technologies Ultra-Low Latency 10G MAC/PCS/PMA Reference Design

The 10G MAC/PCS/PMA IP core can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic, up to jumbo frame size, with no dropped packets.

The cores have been fully verified through extensive Universal Verification Methodology (UVM) based simulations and fully validated on hardware to comply with the IEEE 802.3 standards.

Thanks to their good timing margin performances, the cores are easy to integrate in the XpressGXA10-LP1150 platform. Timing constraints and area placement guidelines are provided with the reference design.

The reference design has been developed using Quartus Prime version 17.1.1.

## **Performance Simulation and Measurements**

This section presents latency and throughput performances under various conditions.

In a dual clock domain configuration, the FPGA simulations demonstrated that the end-to-end round-trip latency is 78ns. Note that the latency performances remain constant regardless of the Ethernet throughput. The next figure presents the round-trip (Tx+Rx) latency results (78.357ns) obtained in simulations for a 64-byte packet (external SERDES loopback).

| 💶 Wave - Default 🖂 🔤        |              |                                  |               |              |            |  |  |

|-----------------------------|--------------|----------------------------------|---------------|--------------|------------|--|--|

| 🖹 • 🗃 🖶 🦈 🎒   👗 🖻           | n 🛍 🖸 😂   🤇  | - м 🗄 🛛 🕸 🖄 🗰 🗸 🐹 🗍              | ᅷ 🏊 🕇   🏦 - 🔝 | 🏦 🛛 🕫 - 🖏 न  | 🖀 • 🧠 📗    |  |  |

|                             |              | , <u>.</u> , <u>.</u> , <u>.</u> |               |              |            |  |  |

| 2.                          | Msgs         |                                  |               |              |            |  |  |

| Input of MAC Tx Path        |              |                                  |               |              |            |  |  |

| ₄> i_Core_Pcs_Clk_p         | 1'h1         |                                  |               |              |            |  |  |

| 👍 o_oti_tx_ready_p          | 1'h1         |                                  |               |              |            |  |  |

| i_oti_tx_vld_p              | 1'h1         |                                  |               |              |            |  |  |

| <pre>4 i_oti_tx_sop_p</pre> | 1'h0         |                                  |               |              | <b>L</b>   |  |  |

| 🚽 🥠 i_oti_tx_eop_p          | 1'h0         |                                  |               |              | _          |  |  |

| 🖬 💠 ivb_oti_tx_bytes_p      | 2'h0         | 2'h0                             |               |              |            |  |  |

| 🖃 🥠 ivb_oti_tx_data_p       | 32'h00160016 | 32'h00000000                     |               | 2'h00000000  |            |  |  |

| — Output of MAC Rx Path —   |              |                                  |               |              |            |  |  |

| nt                          | 1'h1         |                                  |               |              |            |  |  |

| 🖕 o_oti_rx_vld_p            | 1'h1         |                                  |               |              |            |  |  |

| 🔷 o_oti_rx_sop_p            | 1'h1         |                                  |               |              |            |  |  |

| 💠 o_oti_rx_eop_p            | 1'h0         |                                  |               |              |            |  |  |

| 🖃 🖕 ovb_oti_rx_bytes_p      | 2'h0         | 2'h0                             |               |              |            |  |  |

| 💻 👍 ovb_oti_rx_data_p       | 32'h00018828 |                                  |               | 32'h000e000e |            |  |  |

|                             |              |                                  |               |              |            |  |  |

|                             |              |                                  |               |              |            |  |  |

|                             |              |                                  |               |              |            |  |  |

|                             |              |                                  |               |              |            |  |  |

|                             |              |                                  |               |              |            |  |  |

|                             |              |                                  |               |              |            |  |  |

| 🛎 📰 💿 🛛 Now                 | 200000 ns    | liiiilii<br>)00 ns               | 92400 ns      |              | 9280(      |  |  |

| 🔓 🌽 😑 🛛 Cursor 1            | 92423.157 ns | 000113                           | 92423.157 ns  | 78 357 ns    | 32800      |  |  |

| Cursor 2                    | 92501.514 ns |                                  | 92501.        |              |            |  |  |

| 🔓 🎤 😑 🛛 Cursor 3            | 92745.973 ns |                                  |               |              | 745.973 ns |  |  |

| 💼 🎤 😑 🛛 Cursor 4            | 92824.33 ns  |                                  |               |              | 9282       |  |  |

|                             |              | 4                                |               |              |            |  |  |

| 91981940 ns to 94288580 ns  |              |                                  |               |              |            |  |  |

It is important to understand that when a packet is presented to the TMAC it will be transmitted without any back pressure ensuring a deterministic ultra-low latency for any kind of traffic patterns. This is true as long as the TMAC is not driven with traffic rate exceeding 10-Gbps.

The latency performances have also been validated on a REFLEX CES XpressGXA10-LP1150 platform. In order to accurately measure the latency, an electrical loopback plug is inserted into the QSFP+ cage looping the Tx data back into the Rx port. A timestamp is inserted in every transmit packet and compared with the receive packet timestamp. Due to the timestamp

resolution (3.1ns), the latency measurements will always be higher than the real latency (up to 3.1ns extra latency). It is also important to note that some small latency is introduced in the FPGA I/Os, board traces, and QSFP+ loopback module.

The latency measurements are nominally 80.6ns, including the delay introduced in the QSFP+ loopback module. Latency measurements are performed at full throughput with various packet sizes ranging between 64-bytes and 1522-bytes.

The IP core can sustain full throughput without losing any packets while maintaining ultra-low latency performances. Extensive long count tests have been successfully performed to ensure that the cores do not lose any packets under various traffic conditions.

### **Resources Utilization**

The next table presents the resource utilization for one 10G port. The resource utilization for N 10G ports can be calculated by simply multiplying the 1 port resources by a factor of N.

The resources utilization includes the statistics counters.

|                        | ALMS  | ALUTs | Registers | М20К |

|------------------------|-------|-------|-----------|------|

| One 10G MAC/PCS/PMA IP | 3.45k | 3.57k | 5.20k     | 0    |

Table 1: 10G MAC/PCS IP Resources Utilization

## **Performance Monitoring – Statistics**

The 10G MAC/PCS/PMA core has an option to include statistics counters that can be used to provide network performance visibility. Over twenty statistics parameters are available for MAC and PCS in each direction.

A complete list of statistics counters is available in the datasheet and user guide document. Contact Orthogone Technologies for additional information.

## **Technical Support**

Technical support for the IP core is provided for a one year period following the IP licensing date. Extended maintenance and technical support can optionally be purchased on an annual basis after the first year.

Design customization is also available upon request.

# **Board Pricing and IP Licensing Options**

Contact REFLEX CES for XpressGXA10-LP1150 boards pricing information.

The IP core is generally delivered as encrypted source code. Contact Orthogone Technologies to obtain information on licensing fees and to discuss other licensing options. Evaluation licenses are available to simulate and test the cores before purchasing.

# Conclusion

REFLEX CES and ORTHOGONE Technologies closely collaborated to develop a high-performance networking solution specifically designed for applications where latency and throughput performances are critical. This low-profile PCIe Network Processing FPGA card with integrated ultra-low latency 10G MAC enables customers to rapidly integrate their FPGA design into a mature and reliable solution that has been thoroughly tested and verified.

# **ABOUT REFLEX CES and ORTHOGONE TECHNOLOGIES**

#### REFLEX CES

Since 2000, REFLEX CES designs and manufactures custom embedded systems and complex boards based on high-density FPGAs. The company is located in Evry, France and employs 100+ people with R&D and Manufacturing capabilities.

The company provides FPGA COTS boards for several markets, including the Finance market where Ultra Low Latency capability is a key element, and other markets like Networking.

#### Contact Information

Eric Penain, Sales & Marketing – Chief Business Officer Email : <u>epenain@reflexces.com</u> Web site : <u>www.reflexces.com</u>

#### ORTHOGONE TECHNOLOGIES

Orthogone offers a range of electronic design services, including FPGA/ASIC design and verification, HW design, PCB design, software development, and full turnkey electronic product development. The company was founded in 2007 and employs 40+ people at its headquarters in Montreal, Canada. Orthogone Technologies provides ultra-high-performance FPGA/ASIC IP cores used in data centers and networking & communication equipment. The company's IP (Intellectual Property) portfolio includes ultra-low latency and very low gate count Ethernet MAC and PCS solutions operating at 1, 10, 25, 40, and 100-Gbps. Developed by teams of expert FPGA/ASIC designers, Orthogone IP products undergo extensive verification and compliance testing.

#### Contact Information

Alexandre Raymond, VP Product Development Email :<u>araymond@orthogone.com</u> Web site : <u>www.orthogone.com</u>