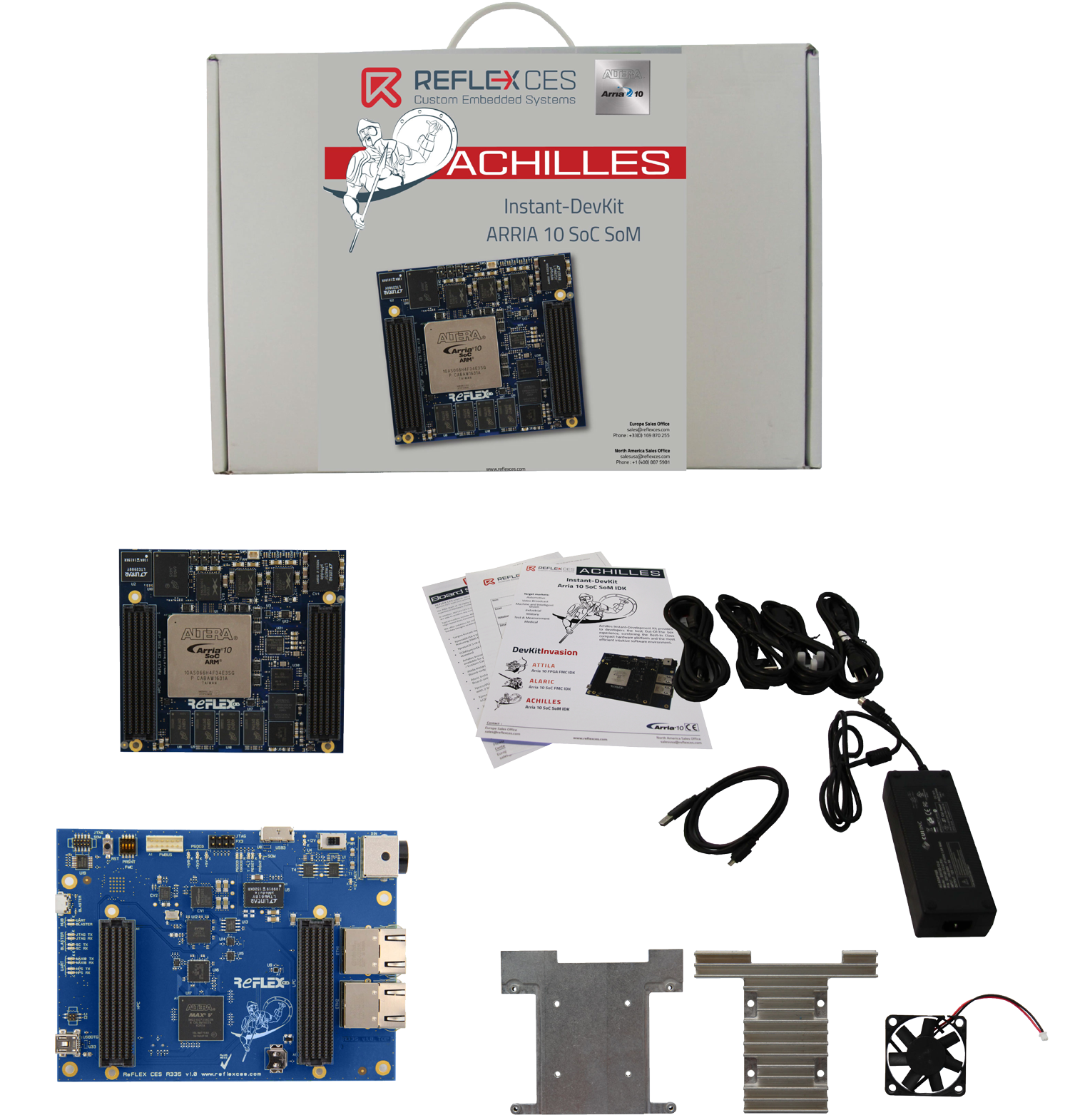

DevKit Achilles

Presentation du DevKit Achilles SoC Arria ® 10

Aperçu du produit

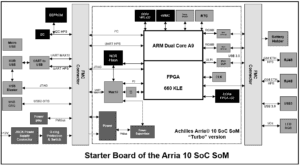

Le DevKit Achilles SoC Arria® 10 est basé sur le FPGA Intel® Arria® 10 SoC. Il comprend le module Achilles Arria® 10 SoC, une starter board, ainsi que tous les schémas et designs de référence utiles pour commencer à travailler avec la carte.

Avec son ARM double-coeur Cortex-A9 MPCore et jusqu’à 660 KLEs dans le FPGA d’éléments logiques à faible consommation, le PFGA Arria® 10 SoC combine la flexibilité et la facilité de programmation d’un CPU avec la configurabilité et la puissance de traitement parallèle d’un FPGA.

Grâce à son SoC (system-on-chip) (un circuit intégré à l’intérieur du FPGA, le plus souvent un processeur CPU – central processing unit), le FPGA peut mieux contrôler la carte.

Sa petite taille et son FPGA puissant le rendent parfaitement adapté aux marchés de l’embarqué et de l’industrie.

Les marchés cibles incluent l’industrie automobile, la diffusion vidéo, la vision intelligente par ordinateur, l’industrie, le militaire, les tests & mesures, et le medical.

Le module Achilles Arria 10 SoC peut aussi être acheté seul. Nous vous proposons aussi en option la carte porteuse PCIe, compatible avec tous nos modules Arria® 10 SoC de reflex ces. Nous pouvons sinon vous concevoir une carte porteuse sur-mesure.

Avantages clés

- FPGA Intel® SoC Arria® 10.

- Taille ultra compacte de 86x95 mm (3.4x3.8 inches), idéal pour des applications en zone contrainte.

- Reference designs disponibles, avec codes source.

- Support Linux Debian standard, pour des portages transparents d'applications software déjà existantes.

La famille de FPGA Intel® SoC Arria® 10 intègre un ARM Cortex-A9 MPCore double-coeur, ainsi que des microcontrolleurs à programmation logique haute-performances, avec transceivers haute-vitesse intégrés.

Le DevKit Achilles de reflex ces offre de nombreuses interfaces selon vos besoins et exigences.

Ce Kit de développement a de nombreux avantages. Il peut être utilisé comme une carte d'évaluation pour commencer à tester votre design, pour réduire votre délai de mise sur le marché. Il peut aussi être utilisé comme une carte de développement, pour faire du prototypage.

Toutes les fiches produits dont vous pourriez avoir besoin seront fournis dans un board support package (BSP). Notre équipe technique est aussi disponible en ligne sur https://support.reflexces.com/

Le FPGA Arria® 10 SoC est un semiconducteur qui permet d'économiser de l'espace sur la carte, avec une densité doublée par rapport à la génération précédente. Cependant, ses besoins énergétiques sont inférieures, et donc sa consommation d'énergie l'est aussi.

le Devkit Achilles est conçu pour une forte productivité, et est parfaitement adapté aux marchés de l'embarqué et de l'industrie.

Notre DevKit Arria® 10 SoC est donc spécialement conçu pour les besoins du client. Notre équipe commerciale est disponible pour vous recommander la meilleure solution en fonction de vos besoins, n'hésitez pas à les contacter sur sales@reflexces.com.

A découvrir sur rocketboards :

- Software BSP le plus récent avec instructions de construction complètes pour les composants logiciels Linux embarqués (u-boot, kernel, rootfs)

- Design de référence FPGA

- BSP complet disponible après l'achat de la carte (documentation et suite complète de designs de référence FPGA)

Specs techniques

Processor

- Dual ARM® Cortex™-A9 MPCore

- Up to 1GHz

- Enhanced with NEON Extension and Single & Double Precision Floating point unit

- 32KB Instruction & 32KB Data L1 Cache

- shared 512KB L2 Cache

- 256KB on-chip Memory

FPGA

- Arria® 10 SX, 10AS066H2F34I1HG, F34 package, speed grade -1

- Logic elements (KLEs) (660)

- M20K memory blocks (2,133)

- M20K memory (Mb) (42)

- MLAB memory (Mb) (5.7)

- GFLOPS (1,519)

FPGA & Soft programming

- AS configuration supported with NOR Flash, remote upgrade support and failsafe functionality: AS, CvP

- eMMC 32GBytes (HPS) / Store U-boot, Kernel and RootFS(8GB on 270 KLE and 32GB on 660 KLE), HPS programming

Control & Ios : Arria® 10 SoC SoM

- 1x USB 3.0 device connectivity using Cypress FX3 super speed controller (660 KLE density)

- 1x USB 2.0 Device/Host

- 1x USB OTG support connected to the HPS

- 2x 10/100/1000 Base-T Ethernet interfaces connected to the HPS

- 1x I²C slave interface (HPS can drive external device)

- 1x UART connected to the HPS ( UART over USB interface)

- 1x UART connected to System controller (MAX10 / UART over USB interface)

- 1x PCIe gen3 x8 Edge interface (Hard IP)

Main interfaces 1.8V FMC VITA 57.1 compliant* :

System-on-Module usage:

- 1x FMC LPC bottom connector with HPS signals and 14 transceivers (Bottom-Right)

- 1x FMC HPC or LPC bottom connector depending on FPGA density (Bottom-Left):

- LPC bottom connector for 270KLE density

- HPC bottom connector for 660KLE density

Carrier board usage with 2 interfaces:

- 1x FMC LPC Top connector with 10 transceivers (Top-Right)

- 1x FMC HPC or LPC Top connector depending on FPGA density (Top-Left):

- LPC Top connector for 270KLE density

- HPC Top connector for 660KLE density

24 Transceivers (up to 11.3Gbps):

- 10x XCVR dedicated to FMC HPC Top connector or to the FMC HPC Bottom connector (Top or Bottom-Left)

- 10x XCVR dedicated to FMC LPC Top connector or to the FMC LPC Bottom connector (Top or Bottom-Right)

- 4x additional XCVR dedicated to the FMC LPC Bottom connector (Bottom-right)

LVDS and LVCMOS

- 80 LVDS bidirectional (or 160 Single ended) on FMC HPC Top connector (Top or Bottom-Left)

- 32 LVDS bidirectional (or 64 Single ended) on FMC LPC Top connector (Top or Bottom-Left)

Memory

- DDR4 HPS (1 bank by 32bit, 4GBytes) @2400MT/s for speed grade -1

- DDR4 FPGA (1 bank by 32bit, 4GBytes) @2400MT/s for speed grade -1

Communications & interfaces : Arria® 10 SoC SoM + starter board Arria® 10 SoC SoM

- Evaluation mode on desk with AC power supply

- 2x Ethernet 10/100/1000 Base-T (HPS)

- 1x USB3.0 Micro B (FPGA)

- 1x USB OTG Mini AB (HPS)

- 1x I²C (HPS)

- 1x UART(HPS) and System Controller interface (through USB connector and MAX 10)

- On-board USB Blaster II

- PMBus interface : Digital Power System management is ready, configure and interrogate the PSM Devices with LTpowerPlay

Power

- Power Management Bus support (PMBus) / cooling solution provided

- Compatible with heat spreader and heatsink (passive or active)

Form factor : Arria® 10 SoC SoM

- Size : 86 mm x 95mm (3.4x3.8 inches)

- 1 x Custom Heat Sink

Form factor : Arria® 10 SoC SoM + starter board Arria® 10 SoC SoM

- Size : 100 mm / 3.94 inches x 140 mm / 5.51 inches

- Fan on top for Starter Kit evaluation mode

Standards and compliance

- RoHS/REACH compliant

- UL certified

- ISO9001 Facility

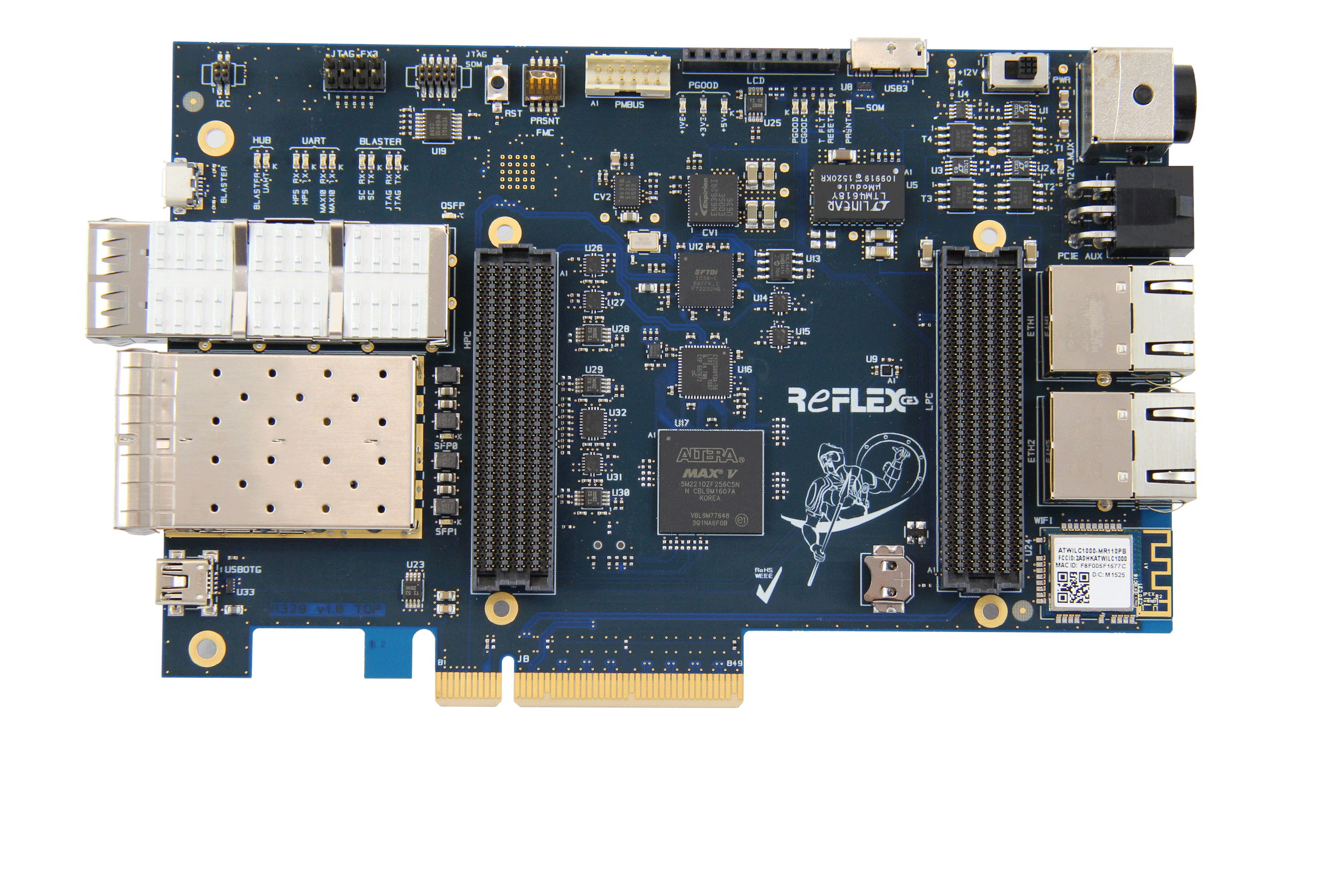

In addition of the Achilles DevKit, you can order the PCIe Carrier Board

* There are four FMC connectors , but the two mirror connectors (Top and Botom on each side) share the same signals, the use of these two connector sis exclusive, one of the two connectors can be used at a time.

Vidéos

Arria® 10 SoC disruptive System-on-Module by REFLEX CES :

Achilles Workshop by REFLEX CES :

Setting up your REFLEX CES Achilles Development Kit :

Exploration of REFLEX CES' Graphical User Interface (GUI) for the Achilles Development Kit :

Object detection demo using FPGA DNN IP :

Livrables

Livrables

- Carte starter avec le module SoC Achilles Arria® 10 (+ répartiteur de chaleur, dissipateur et ventilateur)

- Alimentations et câbles (US, UK, EU, JP), câbles d'interface (USB, Ethernet)

- Documentations du module, de la carte starter, de la carte porteuse PCIe (Manuel de référence, Guide de démarrage)

- Schémas de la carte starter et de la carte porteuse PCIe

- Guide de conception de la carte porteuse

- Dessins mécaniques PDF, 3D Step, fichiers d'assemblage PDF

- Conceptions de test HDL (projets Quartus) par version de module

- RefDesign 10GbE

- Distribution optimisée Kernel Linux & Linaro, bootloader U-boot, scripts de test

- Design software accessible en ligne sur rocketboards

- Support en ligne sur at support.reflexces.com

Informations de commande

- RXCA10S066PF34-IDK0SB: DevKit avec la version du module Achilles Indus v5

Export control ECCN

Numéro ECCN : 4A994i

CECC (commodity Export Classification Certificate) : Télécharger certificat

FAQ

What is the Achilles Instant Devkit?

The Achilles Instant-Development Kit, based on the A10 SoC SoM Turbo version, provides to developers the best Out-Of-The-Box experience, with all the parts that a customer can require to start the System-On-Module.

The Achilles DevKit is delivered with a starter board that provides all the interfaces to communicate with the FPGA and the HPS

-> For more details about the Achilles SoM module main features and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What is included on the Achilles Instant DevKit?

The Achilles Instant-Development Kit includes the following elements:

- Arria® 10 SoC SoM Turbo Version with its custom heat spreader and fan sink

- One Starter board to use the Arria® 10 SoC SoM (find out more on the next question)

- One Power desk adapter (AC/DC), 12V, 108W

- Four Power cables (US, UK, EU, and JP)

- One USB standard cable A-type to Micro USB connector, 1.8 m length

- One USB standard female cable A-type to Mini USB connector B-type

- One USB standard cable A-type to Micro USB3.0, 1m length

- Two Ethernet CAT5E RJ-45 cables

- USB Key: REFLEX innovative software interface (GUI / Windows) with test designs and documentation

- Quartus DKE license (Development Kit Edition Software) One-year evaluation.

What is the Starter board for the Arria® 10 SoC SoM?

When you purchase an Achilles Development Kit, it will also include the Starter board. The starter board includes:

- USB connectors to set up the SoM, JTAG, UART, RJ45 and serial interfaces.

- Onboard USB Blaster JTAG configuration circuitry.

- One µUSB connector allows interfacing UART HPS.

- One connector for connecting a Linear DC1613A USB cable PMBus interface: Drive the digital Power System management on board.

- 0, GPIF II interface fixed at 8 bits on the PHY USB3. Cypress CYUSB3013-BZXC

- 2x 10/100/1000 MBits RJ 45 connector

How many versions of the Arria® 10 SoC SoM exists?

The Arria® 10 SoC SoM offers several versions that depends on the FPGA performances needs and the use of the board.

Lite version: provides the industry’s lowest system cost and power, along with performance levels that makes the device family ideal for differentiating your high-volume applications.

Turbo version: provides high processing capabilities with the 600KLEs and DDR4 high performances levels that makes the device family ideal for complex applications. The dual FMC capabilities allows to interconnect this module very easily with the complete system.

Industrial version: provides industrial temperature product that allows you to use FPGAs and CPLDs, memories and complete design in high-temperature environments, such as automotive telematics, infotainment, and driver assistance systems, as well as temperature-sensitive military and industrial applications.

-> For more details about the module versions and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What is the Dual FMC capabilities of the Achilles SoM ?

The dual FMC capability is the latest idea of REFLEX CES and it takes shape through Achilles : The module can be plugged on a customer carrier board with the two FMC bottom connectors, and offers front panel IO possibilities with a mix of FMC modules plugged on the two FMC Top connectors

The Achilles System-On-Module can be used as FPGA Mezzanine Card & carrier board at the same time!

Do not forget that there are four FMC connectors, but the two mirror connectors (Top and Bottom on each side) share the same signals, the use of these two connectors is exclusive, one of the two connectors can be used one at a time.

Typically, the panel IO functionality was fixed in form factor cards, or it was configured with a fixed front panel IO module. Changing the front panel IO functionality means replacing the complete system. The FMC allows us to create dedicated processing bridge for a wide range of Input / Output data, video , audio, networking and many others signals processing without replacing the all system.

The dual FMC capabilities provides a flexible solution allowing multi configurable I/O front-end for FPGAs

A FMC SoM can provide a flexible solution for custom carrier boards and avoids a long and complicated time to design the digital heart of the system.

A SoM is a highly integrated System-on-Chip module that can be considered as computer-on-module technology coupled with FPGA flexibility for more complex projects.

Which FMC connector do I have to put on my carrier board with the Achilles SoM?

If you design a baseboard on which the Achilles SoC module will be installed, you need to provide SEAF Female connectors (the module is equipped with SEAM on its bottom side)

To obtain a total stack Height of 10 mm between the carrier board and the module, you must use the following reference: SAMTEC P/N: ASP-134486-01 (SEAF-40-06.5-10-A)

To obtain a total stack Height of 7 mm between the carrier board and the module, you must use the following reference: SAMTEC P/N: SEAF-40-05.0-10-A

-> If you want to have a different stack height, you must use the family SAMTEC SEARAY SEAM/SEAF connector; please refer and ask to the REFLEX CES support to know all the possible stack-height

Which FMC connector do I have to put on my FMC mezzanine module with the Achilles SoM?

If you design a Mezzanine board which is installed on Top of the Achilles SoC module, you need to provide SEAM Male connectors (the module is equipped with SEAF on its top side)

To obtain a total stack Height of 10 mm between the carrier board and the module, you must use the following reference: SAMTEC P/N: ASP-134488-01 (SEAM-40-06.5-10-A)

What are the FMC HPC interface TOP pinouts and specifications?

- Power supply: +12V, +3.3V, +Vadj, Vref

- 1 standard signals: Presence, Power Good GA, JTAG, I²C

- Clock distribution with bidirectional and reference clocks: LVDS Clocks, Ref Clocks

- 80 Differential Pairs in three LVDS groups

- (usable 160 single ended)

- HPC: LPC (LA [00:33]) + HA [00:23] + HB [00:21]

- 10 High Speed SERDES, with two SERDES clocks, 10 Gbps

- To avoid power failure, the +1.8V power supply is not provided on the Bottom connector

-> An Excel sheet with legends that describes what kind of signals are connected to the FPGA: LVDS, LVCMOS to standard Bank IOs FPGA, Transceivers to the XCVR bank FPGA, HPS is available upon request: Please contact the sales team to obtain more details on this topic at sales@reflexces.com or go on www.reflexces.com/contact

-> For more details about the FMC pinouts assignment and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What are the FMC HPC interface BOT pinouts and specifications?

- Presence, Power Good GA, JTAG, I²C

- Clock distribution with bidirectional and reference clocks: LVDS Clocks, Ref Clocks

- 80 Differential Pairs in three LVDS groups

- (usable 160 single ended)

- HPC: LPC (LA [00:33]) + HA [00:23] + HB [00:21]

- 10 High Speed SERDES, with two SERDES clocks

- No power supply providing or incoming from this connector

-> An Excel sheet with legends that describes what kind of signals are connected to the FPGA: LVDS, LVCMOS to standard Bank IOs FPGA, Transceivers to the XCVR bank FPGA, HPS is available upon request : Please contact the sales team to obtain more details on this topic at sales@reflexces.com or go on www.reflexces.com/contact

-> For more details about the FMC pinouts assignment and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What are the FMC LPC interface TOP pinouts and specifications ?

- 1 standard signals: +12V, +3.3V, +Vadj, Vref Presence, Power Good GA, JTAG, I²C

- Clock distribution with bidirectional and reference clocks: LVDS Clocks, Ref Clocks

- 33 Differential Pairs in one LVDS group

- (33 pairs +2 single ended)

- (usable 68 single ended)

- HPC: LPC (LA [00:33])

- 10 High Speed SERDES, with Two SERDES clocks

- No HPS interface

-> An Excel sheet with legends that describe what kind of signals is connected to the FPGA: LVDS, LVCMOS to standard Bank IOs FPGA, Transceivers to the XCVR bank FPGA, HPS is available upon request. Please contact the sales team to obtain more details on this topic.

-> For more details about the FMC pinouts assignment and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What are the FMC LPC interface BOT pinouts and specifications ?

- Power supply Input: +12V

- 1 standard signals: Presence, Power Good GA, JTAG, I²C

- Clock distribution with bidirectional and reference clocks: LVDS Clocks, Ref Clocks

- 33 Differential Pairs in one LVDS group

- (33 pairs +2 single ended)

- (usable 68 single ended)

- HPC: LPC (LA [00:33])

- 14 High Speed SERDES, with Two SERDES clocks

- Full HPS interface accessible by this connector

- SoM A10 Power supply input from this connector

-> An Excel sheet with legends that describe what kind of signals is connected to the FPGA: LVDS, LVCMOS to standard Bank IOs FPGA, Transceivers to the XCVR bank FPGA, HPS is available upon request. Please contact the sales team to obtain more details on this topic.

-> For more details about the FMC pinouts assignment and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

How can I connect my FPGA carrier board with the FMC cable?

You need to use the SEARAY™ High-Speed High-Density Array Cable Assembly from Samtec. Please refer to the SAMTEC web page HDR Cable Assembly Options for FMC to know all the interconnect possibilities.

What is the PCIe carrier board and can I use the Arria® 10 SoC SoM on it?

This PCIe Carrier Board is an optional extra product for clients looking for a PCIe format board.

REFLEX CES Arria® 10 SoC module can be plugged on this PCIe Carrier Board. The PCIe carrier board then provides access to all of the features of the System-On-Module:

- USB connectors to set up the SoM, JTAG, UART, RJ45 and serial interfaces.

- Onboard USB Blaster JTAG configuration circuitry.

- One µUSB connector allows interfacing UART HPS.

- One connector for connecting a Linear DC1613A USB cable PMBus interface: Drive the digital Power System management on board.

- 0, GPIF II interface fixed at 8 bits on the PHY USB3. Cypress CYUSB3013-BZXC

- 2x 10/100/1000 MBit RJ 45 connector

It also provides access to further functions, including:

- QSFP+: Quad Small Form-factor Pluggable up to 4 lanes at 10.3125 Gbps

- SFP+: Small Form-factor Pluggable with 1 lane at 10.3125 Gbps

- PCIe x8 Gen3: Hard IP PCIe implemented and rooting to enable lanes at 8 Gbps

- Wifi solution with the Atmel IEEE 802.11 b/g/n Link Controller SoC

The PCIe carrier board is delivered with schematics and VHDL test designs

-> For more details about the Achilles Instant DevKit and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

Which kind of DDR4 memory and architecture are embedded on the Achilles Module?

You will have two independent memory banks with four chips with density 8Gb or 16Gb each bank : each memory bank of the Arria® 10 SoC SoM address a 32 bits data bus width by using two chip x16bits, with a clock rate at 1200MHz or 2666MHz (according to the module version)

A test design that validates the DDR4 memory connected to the FPGA is available, it uses the Intel example design generated with the DDR4 controller IP.

The final user can use the memory bank connected physically to the HPS without using the HPS to add this memory interface to the FPGA. The DDR4 interface of the HPS uses the Bank IO, shared with the FPGA, and that can be used by the FPGA only. If the HPS is alive, the DDR4 is normally used to execute the Operating system pattern and cannot be used as additional memory interface to the FPGA.

What are the cooling options on the System-On-Module?

Already mounted, the thermal solution is composed of two parts: Heat spreader and Heat sink, that offers air-cooled and conduction-cooled solutions depending of the customer environment.

If you want to use the SoM A10 in standalone application, on a desk or ambient environment without mechanical constraint, you can leave the FAN top of the set and ensure a good cooling solution.

If you want to integrate the SoM A10 into an enclosure, a server, or a custom rack, you need to evaluate the operating range temperature with requirements in terms of airflow. The heatsink can be upgraded by customization, to offer better airflow evacuation.

For highly constrained industrial environments, please refer to industrial version of the SoM, called “industrial”

What is the carrier Design Guide (CDG)?

This document provides information for designing a custom Carrier Board for the Arria® 10 SoC SoM Module. It includes reference schematics for the external circuitry, required to implement the different interfaces available on the module.

This design guide is intended for electronics engineers designing a carrier board for the Arria® 10 SoC SoM. In most cases, the examples come from designs that have been built and tested.

The CDG gives a list of suggestions for designing with high-speed differential signals and single ended signals:

- Use controlled impedance PCB traces.

- Keep the trace lengths.

- Trace-length constraints, separation, group matched

- Clocks/periodic signals (CMOS/TTL) recommendations

- Route differential signals and PCB layers, Routing Considerations

What is the performance of the USB3.0?

The PHY component is connected to the Core Fabric of the Arria® 10 SX, the GPIF II interface is fixed at 8 bits on the PHY. This enables interface frequencies up to 100 MHz so a maximum work data rate of 800 Mb/s data rates after encoding, corresponding to High-Speed mode.

In case of redesign or creation of a similar interface by using the FMC interfaces, we advise to use the complete data bus of the FX3 by using the 32 bits to provide SuperSpeed solution with a symbol rate up to 5 Gbit/s for an effective data rate at 4 Gbit/s (500 MB/s).

How can I supply power to the Arria® 10 SoC SoM?

When using the module alone without using our Starter board, you can supply the SoM A10 with an input voltage in the range of +5.5V-17V.

The components at the top in the power supply tree can absorb an input up to +17V. But, in this case, you will not be able to connect FMC modules to the TOP connectors of the module because VITA57.1 imposes a maximum of + 12V +/- 5%. In addition, to offer the input voltage for the internal power tree, we connect the + Vin directly to the pins of the FMC connectors. So be careful when designing your own power supply input and limitation.

When using a starter board or PCIe carrier board designed by REFLEX CES, you will see that we have a protective, surge and reverse mounting. You will be able to supply an input voltage in the range of + 9.5V-13.45V

How to specify the external power supply input?

Concerning the Arria® 10 SX SoM, we use power supply unit with a CUI INC AC adapter:

P/N: SDI120-12-U

Input: 100-240V ≈ 47-63Hz 2.8A Max

Output (DC): 12V / 9 A => 108W

LTM4675 Power rail:

First stage of the Power supply tree, the DC/DC converter has ADC inside that allows it to measure the output voltage and has also PMBus driver to communicate on the PMbus. We can monitor the power supply input +12V and the output voltage from this component which provide the primary power rail +5V.

-> For more details about the power supply of the Achilles SoM module and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What does the Power Management Bus (PMBus) is used for?

The Power Management Bus (PMBus) is a standard power-management protocol. This flexible and highly versatile standard allows communications between devices, based on both analog and digital technologies. It is a standard way to communicate with power Converters and FPGA over a Digital communications Bus. It is similar to the I²C protocol.

Below, you will find the list of the channels which are monitored and managed by the CPLD MAX 10 or external operator with the DC1613A through PMBus connector (available on the Starter board or the PCIe carrier board):

LTC2980 Power supervisor device A :

channels 0: 3V3 U

channels 1: 3V3 I (Rshunt = 10 mohms)

channels 2: 2V5 U

channels 3: 2V5 I (Rshunt = 510 mohms)

channels 4: VTT_DDR4 U (0.6V)

channels 5: no current on this channel

channels 6: VDDQ U

channels 7: VDDQ I (Rshunt = 100 mohms)

LTC2980 Power supervisor device B :

Channels 0: 0V9 U

Channels 1: 0V9 I (Rshunt = 5 mohms)

Channels 2: 0V95 U

Channels 3: 0V95 I (Rshunt = 10 mohms)

Channels 4: 1V2 U

Channels 5: 1V2 I (Rshunt = 30 mohms)

Channels 6: 1V8 U

Channels 7: 1V8 I (Rshunt = 10 mohms)

LTM4675 Power rail :

First stage of the Power supply tree, the DC/DC converter has ADC inside that allows it to measure the output voltage and has also PMBus driver to communicate on the PMbus. We can monitor the power supply input +12V and the output voltage from this component which provide the primary power rail +5V.

How can I work with the MAX 10 FPGA on board?

MAX® 10 FPGAs allows non-volatile integration, with NOR flash technology inside the device. Unlike CPLDs, MAX 10 FPGAs also includes full-featured FPGA capabilities, such as Nios® II soft core embedded processor support, digital signal processing (DSP) blocks.

With the Arria® 10 SoC SoM, the Max10 CPLD is used as an on-board system control which manage the voltage, temperature, power good, JTAG and communicate with the FPGA and the extremal world through UART and I²C link.

-> For more details about the power supply of the Achilles SoM module and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

Which ways of programming do I have on Arria® 10 SoC SoM?

In the Arria® 10 SoC, several boot configurations are possible:

- The HPS boot and FPGA configuration occurs separately (Achilles devkit configuration)

- The HPS boots first and configures the FPGA

- The HPS boots from the FPGA after the FPGA is configured

Scenario 1 : You can program the Arria® 10 FPGA and (or) the MAX 10 through USB blaster in JTAG mode.

Scenario 2 : At power-up, Arria® 10 FPGA automatically loads via a quad serial interface with its dedicated NOR FLASH, in AS configuration mode.

Scenario 3 : After having initialized the HPS, the BootROM determines the device where the bootloader is stored using the BSEL pins ( NAND, QSPI, µSD…the FPGA IOs can be used)

Scenario 4 : After having initialized and ready to use the HPS, can load a bitstream from external , as GbE and program the FPGA

Scenario 5 : “Configuration via Protocol” : One minimal configuration is contained in the NOR Flash. This binary is loaded in the FPGA allowing the improvement of the PCIe access and permits the software to load external image in the Arria® 10

-> For more details about the programming of the Achilles SoM module and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

How do I manage the Clocks into the SoM?

The programming Clock Generator is a highly flexible and configurable clock generator/buffer. This component provides special and high-quality clock signals for high-speed transceivers. The clock generator Si5341 Rev D from Silicon Labs is controlled by the MAX10 through an I²C serial interface. The user can modify the frequency between 0.0001 MHz to 1.024 GHz

The clock transceivers corresponding to interface links are connected to three different transceivers banks, each featuring two reference clock inputs. At least one reference clock input per bank is fed by the same programmable PLL with a maximum skew of 100ps.

DDR4 controller reference clock input is also fed by the Si5341.

A test design, included in the board package, demonstrates the configuration of the SI5341. It uses a VHDL module which reads data from an internal RAM block and performs I²C accesses to configure the clock generator registers.

The RAM content is generated with a custom converter tool taking as input a ClockBuilder Pro project exported file. This allows performing any kind of configuration:

- Setting output clock frequencies

- Switching from input clock source

-> For more details about the clock circuitry of the Achilles SoM module and to get documentation, please email sales@reflexces.com or go on www.reflexces.com/contact

What hardware development tools are available?

Intel ‘s Qsys system integration tool saves you time and effort in the FPGA design process, simplifying the development of complex hardware systems by automatically generating an FPGA-optimized network-on-chip interconnect, system Testbench, simulation model, software header file, and data sheet to expedite development across hardware and software teams. Qsys supports industry-standard interfaces, including ARM AMBA® AXITM, Avalon® Memory-Mapped, and Avalon Streaming interfaces.

Intel offers a broad portfolio of IP including embedded, interface protocol, video, image processing, DSP, and memory controller cores that can be integrated with user-designed IP to create a custom ARM processor system.

How do the FPGA and the HPS communicate?

The HPS shares the high-bandwidth interconnect backbone, capable of over 100-Gbps peak throughput, consisting of two 128-bit AMBA AXI bus bridges. IP built in the FPGA fabric have access to HPS bus slaves via the FPGA-to-HPS bridge. Similarly, HPS bus masters have access to bus slaves in the FPGA fabric via the HPS-to-FPGA bridge.

Does your FPGA test designs includes any HPS examples?

To build and debug HPS software, the suite of Intel design tools, Intel SoC Embedded Design Suite (SoC EDS), needs to be installed. The version to use is the Intel SoC EDS v16.1.0.196.

We provide all parts that the user needs to build his own software architecture:

- The processor executes the 128 KB BootROM code which resides inside on-chip ROM. The main role of the BootROM is to initialize all required hardware components to boot up the next stage boot software, the U-Boot bootloader.

- The bootloader used in the devkit is U-Boot, an open source bootloader used in many embedded devices.

- The Operating System running on the HPS is Linux. So, the boot image loaded by U-boot is the kernel image. It is responsible for supporting all the hardware of the Achilles devkit handled by the HPS. The version used is a customized 4.1.22.

- We provide two different root file systems to be mounted by the Linux kernel on the HPS:

- One is based on the Linaro-nano release based on Ubuntu 15.04. It has been customized to add SSH support, network setup and HPS test scripts and programs.

- The second one is built with Buildroot and based on Busybox.

What is the size of the Arria® 10 SoC SoM?

The size of the SoM is 86mm x 95 mm

The figures into the Carrier design Guide documentation shows the Arria® 10 SoC SoM form factor with connector and attachement holes position, views from the TOP side of the board, dimensions in millimeters. Detailled STEP File of the Arria® 10 SoC SoM is available upon request, please contact support or your sale representative for more information.